#### Strutture a bande:

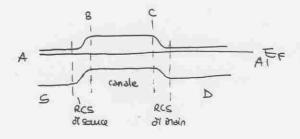

consideriemo i hodo AAI

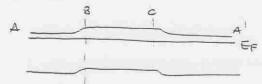

All'equilibrio, une con Vs = VD = VG = VB = \$

Applicando Voro:

Infine, applicando Vo 70 e guardando à diagramma. bonde lingo x:

inc y=L

$$V_G - V_{ox} = \psi_S + V_D$$

$$\Rightarrow \psi_S = V_G - V_{ox} - V_D$$

cioe :

e lungo y

sint

qVo D int

canale

In presenza di cariche nell' ossido e/o di  $\phi$ MS  $\neq$  0, la tensione di soglia viene modificata a causa del contributo di VFB, che rappresenta la tensione che occorre applicare al gate per portare il sistema nella condizione di banda piatta. In pratica, a tensione di gate nulla, le bande non sono piatte, ovvero all' interfaccia tra ossido e semiconduttore si concentra una certa quantità di carica (per accumulo o per svuotamento, a seconda del segno di VFB) e occorre applicare una tensione  $\neq$  0 al gate per riportare il sistema in questa condizione.

The state condition is:

$$V_{T} = V_{FB} + \frac{qN_{A}W_{m}}{C_{o}} + \psi_{inv} =$$

$$= V_{FB} + \frac{\sqrt{2\varepsilon_{S}qN_{A}(2\psi_{B})}}{C_{o}} + 2\psi_{B}$$

$$V_{FB} = \Phi_{MS} - \frac{Q_{ox}}{C_{ox}} \frac{x}{d} = \Phi_{MS} - \frac{Q_{it} + Q_f + Q_{ot} \pm Q_m}{C_{ox}} \frac{x}{d}$$

Esistono dei grafici ricavati sperimentalmente che forniscono direttamente il valore della tensione di soglia al variare del drogaggio (da notare che si riferiscono a specifiche condizioni di spessore dell' ossido, ovvero di Cox, e di materiale che costituisce il gate, ovvero di φMS).

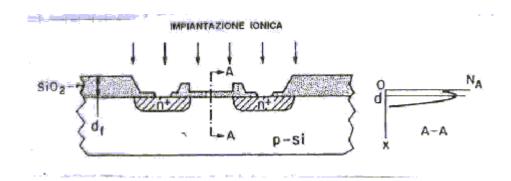

In effetti un modo pratico per ottenere dispositivi con diverse tensioni di soglia è proprio quello di variare il drogaggio, anche solo localmente con dei procedimenti di impiantazione ionica che viene realizzata nella regione di canale per uno spessore limitato di semiconduttore, lasciando tutto il resto del semiconduttore invariato.

Un ruolo importante nella determinazione della tensione di soglia è rivestito dalla capacità dell' ossido.

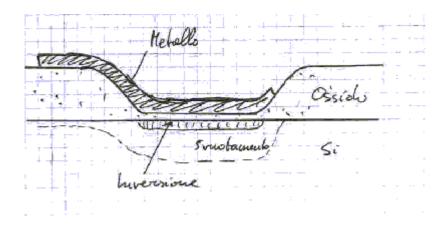

Più l' ossido è spesso e minore è la capacità, ragion per cui le regioni del chip esterne alla regione in cui viene fabbricato un mosfet vengono sempre ricoperte da uno strato di ossido sufficientemente spesso da garantire che le tensioni presenti sulle piste metalliche che ne percorrono la superficie non possano accidentalmente produrre inversione di popolazione negli strati di silicio sottostanti.

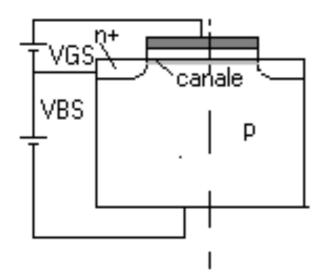

Infine, VT può essere modificata applicando un' opportuna tensione al substrato (a condizione che sia contattabile).

Necessariamente, la tensione applicata al substrato (B = Bulk), come sempre riferita al Source (VBS), deve essere tale da non mandare in diretta le due giunzioni pn formate rispettivamente con Source e Drain. In un MOSFET a canale n, di solito viene applicata al bulk la più bassa tra le tensioni applicate agli altri terminali (ovvero tensioni  $\leq 0$ ), mentre in uno a canale p la tensione più alta (ovvero tensioni  $\geq 0$ ).

Ma variando nel range permesso la tensione di bulk si va in realtà a modificare localmente il potenziale del semiconduttore, portando più in inversa le giunzioni di source e drain, quindi ampliando (a parità di tutte le altre tensioni applicate al sistema) la regione di svuotamento che circonda le diffusioni di source e drain.

Fissiamo l'attenzione su una metà del dispositivo

Supponiamo che inizialmente VBS = 0 e sia VGS tale da indurre nel semiconduttore la zona di inversione. Questo significa che all' interfaccia tra semiconduttore e ossido ci sarà un certo valore di potenziale,  $\psi x$  (>2  $\psi B$ ), che assicura lo stato di inversione del semiconduttore. Se ora applichiamo VBS <0, risulta che al source ci sia un potenziale positivo rispetto al bulk ovvero attrattivo per gli elettroni del canale, che possono uscire dal canale e riversarsi nel contatto di source. Perciò, pur non essendo variato VGS, il canale si trova "meno in inversione" rispetto al caso VBS = 0. Per ripristinare la situazione iniziale occorre perciò aumentare VGS. Di quanto? Per capirlo possiamo ragionare in questo modo:

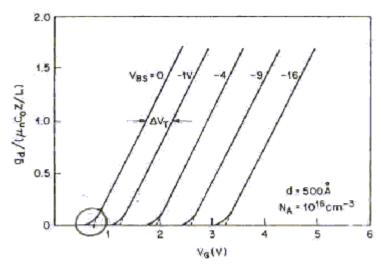

Fig. 5.43 Regolazione della tensione di soglia mediante polarizzazione del substrato

Quando si applica VGS al gate, si induce sul gate una carica positiva che viene compensata dalla carica negativa del semiconduttore, contenuta in parte nel canale (costituita da elettroni) e in parte nella regione svuotata (costituita da ioni accettori). Applicando VBS si aumenta la carica della regione svuotata a spese della carica del canale (visto che la carica di gate da compensare rimane la stessa) e perciò attraverso l' espressione della carica indotta nella regione di svuotamento in funzione della tensione, si può risalire al nuovo valore della tensione di soglia.

$$Q_{B} = -\sqrt{2q\varepsilon_{S}N_{A}(2\psi_{B} - V_{BS})}$$

$$\Delta V_{T} = \frac{\sqrt{2q\varepsilon_{S}N_{A}}}{C_{CT}}(\sqrt{2\psi_{B} - V_{BS}} - \sqrt{2\psi_{B}})$$

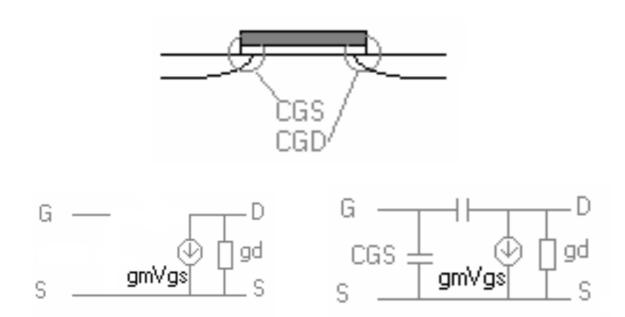

Il circuito equivalente del MOSFET è pressochè identico a quello di tutti i transistor ad effetto di campo.

Nel caso del MOSFET, le possibili sovrapposizioni tra il contatto di gate e le diffusioni di Source e Drain, generano degli effetti di capacità parassita che si traducono nei corrispondenti componenti del circuito equivalente.

In particolare, CGD genera un percorso di ritorno tra uscita e ingresso che modifica l'idealità della risposta in frequenza del dispositivo.

Per valutare l'amplificazione prodotta dal dispositivo su un segnale alternato in ingresso pari a  $i_{in}$ , occorre fare il rapporto tra  $i_{out}$  e  $i_{in}$ .

$$\begin{aligned}

\dot{i}_{in} &= j\omega(C_{GS} + C_{GD}) V_{in} \\

\dot{i}_{out} &= g_m V_{in} \\

\begin{vmatrix} \ddot{i}_{out} \\ \ddot{i}_{in} \end{vmatrix} &= \frac{g_m V_{in}}{\omega(C_{GS} + C_{GD}) V_{in}} = \frac{g_m}{\omega(C_{GS} + C_{GD})}

\end{aligned}$$

Si noti che le correnti di ingresso e uscita vengono valutate mettendo in corto circuito rispettivamente l'uscita e l'ingresso. Il rapporto ottenuto dipende dalla frequenza. Si definisce una frequenza di taglio in corrispondenza della quale il rapporto vale 1 e l'uscita non risulta quindi più amplificata rispetto all'ingresso.

$$\frac{\dot{i}_{out}}{\dot{i}_{in}} = \frac{g_m}{\omega(C_{GS} + C_{GD})} = 1$$

$$\omega_T = \frac{g_m}{(C_{GS} + C_{GD})}$$

$$f_T = \frac{g_m}{2\pi(C_{GS} + C_{GD})}$$

Perciò, per massimizzare fT, occorre cercare di minimizzare la capacità vista dalla maglia di ingresso (schematizzata con i due contributi CGD e CGS). L'origine fisica della capacità complessiva vista all'ingresso è data dalla capacità dell'ossido, in parallelo con le eventuali sovrapposizioni tra il gate e le altre due diffusioni. Perciò, è opportuno cercare di evitare questi contributi parassiti e allineare perfettamente il gate alle diffusioni.

In caso di allineamento perfetto, si ha, in zona lineare:

$$f_{T} = \frac{g_{m}}{2\pi C_{c}} = \frac{1}{2\pi} \frac{Z}{L} \mu_{n} C_{o} V_{D} \frac{1}{C_{o} Z L} = \frac{\mu_{n} V_{D}}{2\pi L^{2}} V_{D} < V_{Dsat}$$

Perciò, il criterio pratico per ottenere frequenze di taglio più alte possibili, oltre a quello di minimizzare le sovrapposizioni (capacità parassite) è quello di cercare di ottenere alte mobilità dei portatori nel canale e canali corti.

Per quanto riguarda la capacità ideale di gate, che abbiamo sbrigativamente posto pari alla capacità dell'ossido, dovremmo in realtà ricordare che la capacità complessiva è in realtà data da una serie di due capacità, quella dell'ossido e quella della regione di svuotamento del semiconduttore. Quando il canale è formato la capacità equivalente del sistema risulta in effetti essere coincidente con quella dell'ossido ma se andiamo a vedere la curva capacità-tensione del sistema MOS, potremmo osservare che l'andamento non è uniforme al variare della frequenza.

Nel caso del MOSFET, invece, la curva capacità –tensione non dipende più dalla frequenza. La causa di ciò risiede nel fatto che nel MOSFET gli elettroni che vanno a formare il canale non provengono dalla regione di bulk, ma dalle due diffusioni n+ di source e drain.Perciò, gli elettroni provengono da regioni in cui sono maggioritari e non risentono di fenomeni "lenti" che ne rendano non istantanea la risposta dei portatori alle variazioni di tensione. Corrispondentemente, la curva capacità –tensione di un MOSFET coincide con la curva a bassa frequenza del MOS.

# Considerazioni sulla polarizzazione del MOSFET in applicazioni circuitali

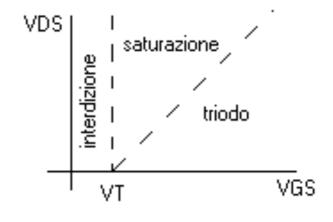

Consideriamo la caratteristica di uscita di un MOSFET a canale n ad arricchimento.

Per lavorare nella regione di triodo, occorre prima indurre un canale, applicando una tensione di gate superiore alla tensione di soglia e poi occorre mantenere VDS abbastanza piccolo da non indurre lo strozzamento del canale, ovvero:

$$V_{DS} < V_{DSsat} = V_{G} - V_{T}$$

$$I_{DS} = k[2(V_{GS} - V_{T})V_{DS} - V_{DS}^{2}]$$

$$k = \frac{1}{2}\mu_{n}C_{ox}\frac{Z}{L}$$

In saturazione:

$$V_{GS} > V_{T}$$

$$V_{DS} > V_{GS} - V_{T}$$

$$I_{DS} = k(V_{GS} - V_{T})^{2}$$