# Corso di Tecnologie e Dispositivi Elettronici Avanzati A.A. 2016/2017

#### Prof. Piero Cosseddu

Dept. Of Electrical and Electronic Engineering University of Cagliari (Italy)

email: piero.cosseddu@diee.unica.it

url: <a href="http://people.unica.it/pierocosseddu">http://people.unica.it/pierocosseddu</a>

http://sites.unica.it/dealab

# Il transistor ad effetto di campo Metal Oxide Field Effect Transistor (MOSFET)

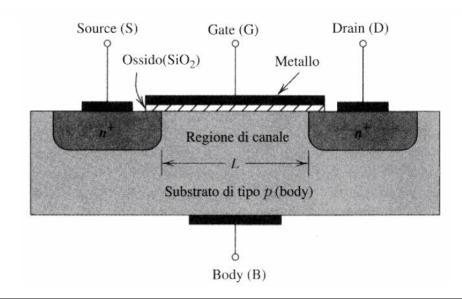

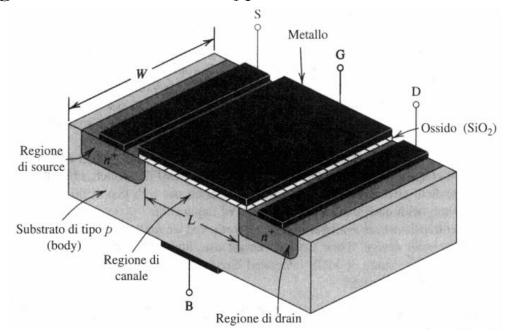

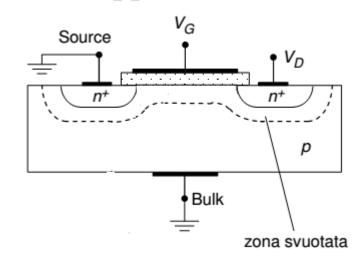

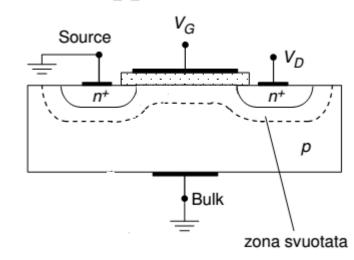

- Cuore della struttura MOS a substrato p

- Due diffusioni n+, due ulteriori contatti, SOURCE e DRAIN

- Il contatto del bulk può essere (ma non obbligatoriamente) eliminato.

- L'elettrodo di gate è elettricamente isolato dal resto della struttura attraverso l'ossido della struttura MOS.

- Viene polarizzato mantenendo il source collegato a massa, ovvero viene adottata una configurazione "a source comune"

I parametri geometrici da considerarsi sono:

- La lunghezza del canale L

- La larghezza di canale W

- Lo spessore dell'ossido *d*,

- La profondità della giunzione  $r_j$

- Il drogaggio del substrato  $N_A$

Ossido con R infinita

Diffusioni n+ fortemente drogate

Perché non scorre corrente pur

applicando un Vds?

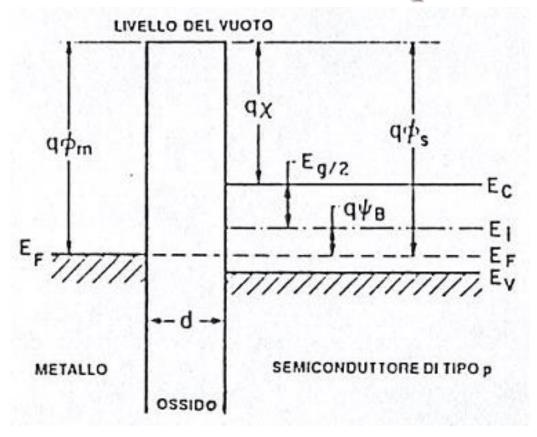

#### Il sistema Metallo Ossido Semiconduttore (MOS)

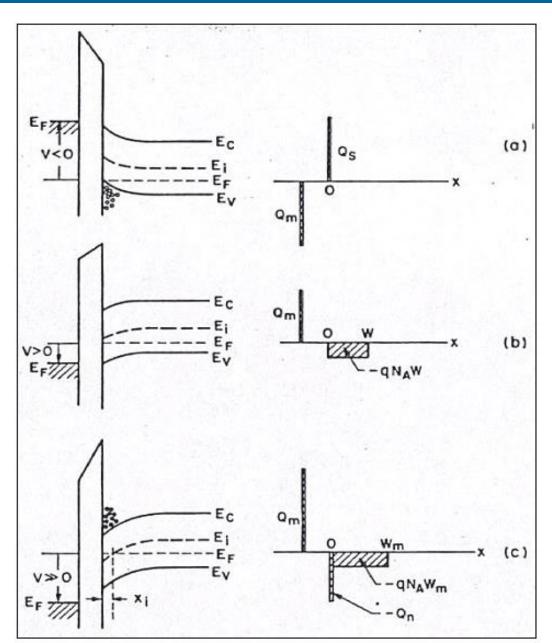

## condizione di banda piatta

- Cosa rappresenta l'energia di Fermi?

- Cos'è la funzione lavoro?

#### Il sistema Metallo Ossido Semiconduttore (MOS)

Cosa succede se non applichiamo alcuna tensione al gate?

Circuito aperto

Perché?

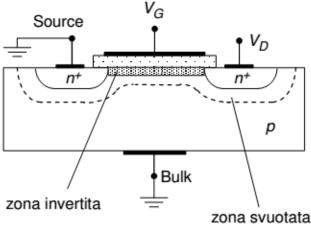

Se applico una tensione di gate positiva, ma piccola, la regione di svuotamento aumentanta, se Vg>Vt creo il canale

n

**a)**

$$V_D = 0$$

## Tensione di soglia nel MOS

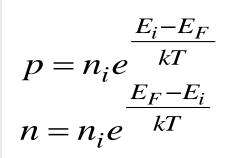

Tensione di soglia  $(V_T)$  è tale da generare un potenziale superficiale pari a quello di forte inversione,  $\psi_S = \psi_{S,inv}$

Essendo inoltre la carica per unità di area ad essa corrispondente e  $qN_AW_m$ , varrà

$$V_{T} = \frac{qN_{A}W_{m}}{C_{o}} + \psi_{inv}$$

$$= \frac{\sqrt{2\varepsilon_{S}qN_{A}(2\psi_{B})}}{C_{o}} + 2\psi_{B}$$

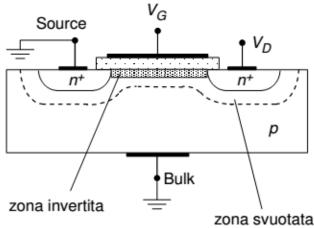

#### Non idealità nel MOS

La carica nell'ossido induce capacitivamente carica nel semiconduttore. Se la carica si trovasse tutta all'interfaccia tra ossido e semiconduttore, il contributo alla tensione di banda piatta sarebbe pari a:

$$V_{FB} = \Phi_{MS} - \frac{Q_{ox}}{C_{ox}}$$

La carica però potrebbe non necessariamente essere concentrata tutta all'interfaccia

$$V_{T} = \frac{\sqrt{2\varepsilon_{S}qN_{A}(2\psi_{B})}}{C_{o}} + 2\psi_{B} + \left[\phi_{MS} - \frac{Q_{ox}}{C_{ox}}\frac{x}{d_{ox}}\right]$$

# II PMOS con $V_{FB} \neq 0$

In generale abbiamo:

$$\begin{aligned} V_T &= -\frac{\sqrt{2\varepsilon_S q N_D(2\psi_B)}}{C_o} - 2\psi_B + V_{FB} \\ V_T &= -\frac{\sqrt{2\varepsilon_S q N_D(2\psi_B)}}{C_o} - 2\psi_B + \left[ \phi_{MS} - \frac{Q_{ox}}{C_{ox}} \frac{x}{d_{ox}} \right] \end{aligned}$$

Cosa succede se non applichiamo alcuna tensione al gate?

Circuito aperto

Perché?

Se applico una tensione di gate positiva, ma piccola, la regione di svuotamento aumentanta, se Vg>Vt creo il canale

n

**a)**

$$V_D = 0$$

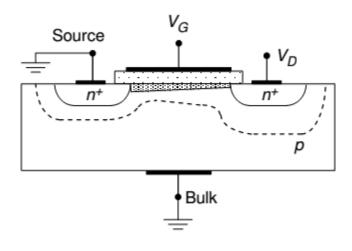

#### Cosa è il pinch off?

Se applico una  $V_{\rm DS}$  il canale diventa sempre meno simmetrico e si restringe verso il drain.

In effetti,  $V_{GD}=V_{GS}-V_{DS}$ , se aumenta  $V_{DS}$ ,  $V_{GD}$  diminuisce

Diminuisce la concentrazione di elettroni vicino al drain

Se  $V_{GD}=V_{T}$  sono al limite tra inversione e svuotamento il canale si strozza, pinch-off

**b)**

$$0 < V_D < V_G - V_T$$

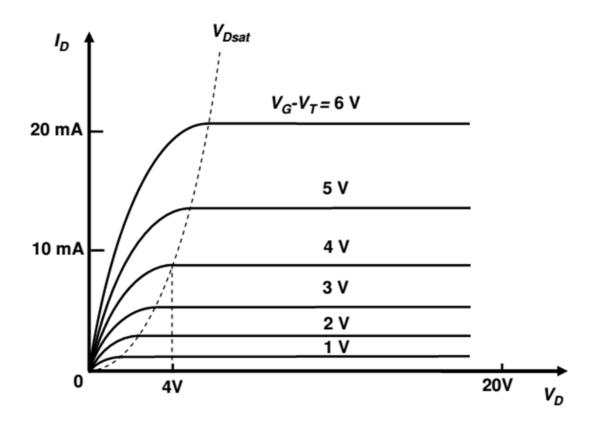

#### Identifichiamo 3 regioni di funzionamento

- 1. V<sub>GS</sub><V<sub>Th</sub> regione di interdizione

- 2.  $V_{GS}>V_{Th}$  e  $V_{DS}<V_{GS}-V_{Th}$  regione lineare o di triodo

- 3.  $V_{GS}>V_{Th}$  e  $V_{DS}>V_{GS}-V_{Th}$  regione di saturazione

# Il sistema MOSFET: regione lineare

$$I_D \cong \frac{Z\mu_n}{L} C_{ox} \left[ V_G - V_T - \frac{V_D}{2} \right] V_D$$

$$g_D = \frac{\partial I_D}{\partial V_D}\Big|_{V_T = \cos t} = \frac{Z\mu_n}{L} C_{ox} [V_G - V_T]$$

conduttanza

$$g_m = \frac{\partial I_D}{\partial V_G}\Big|_{V_D = \cos t} = \frac{Z\mu_n}{L} C_{ox} V_D$$

transconduttanza

# Il sistema MOSFET: regione di saturazione

$$I_{Dsat} = \frac{Z\mu_n}{2L} C_{ox} (V_G - V_T)^2$$

$$g_{msat} = \frac{Z\mu_n}{L} C_{ox} (V_G - V_T) = g_{dlin}$$

$$g_D = \frac{\partial I_D}{\partial V_D} \bigg|_{V_G = \cos t} = 0$$

Pinch off

$$V_D \ge V_{Dsat} = V_G - V_T$$

transconduttanza

conduttanza

La conduttanza è data dalla pendenza della caratteristica di uscita in regione lineare Dipende dalla Vg

La transcoduttanza in regione lineare è costante per una data Vd

È la pendenza della transcaratteristica

La transconduttanza in regione di saturazione dipende da Vg, ma non da Vd!

È la pendenza della retta tangente alla transcaratteristica per un determinato valore di Vg

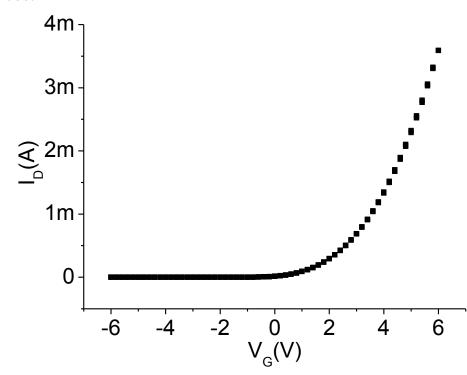

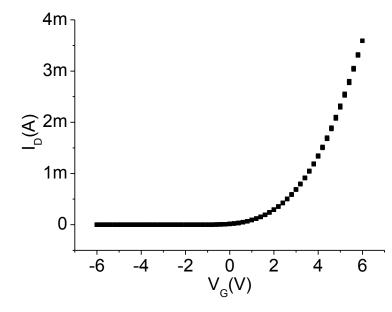

# Come posso determinare la tensione di soglia e la mobilità dalle curve del transistor?

$$I_D = \frac{Z\mu_n}{L} C_{ox} [V_G - V_T] V_D$$

Regime lineare

$$I_D = \frac{Z\mu_n}{2L} C_{ox} (V_G - V_T)^2$$

Regime di saturazione

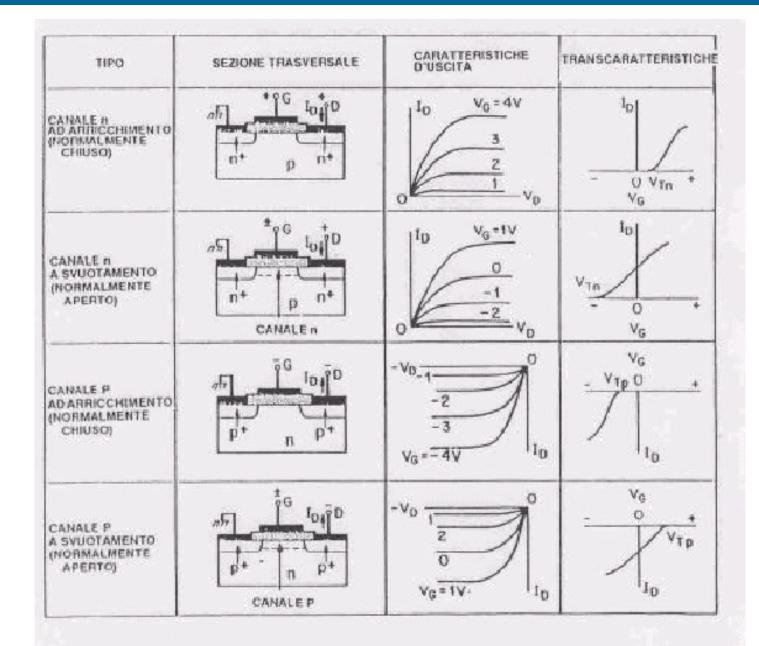

A seconda che il semiconduttore sia di tipo p o di tipo n e a seconda del valore della tensione di soglia, si possono ottenere diversi tipi di dispositivi che si distinguono in base al fatto che a V= 0 V, il canale sia o meno formato e al tipo di conduzione (tramite elettroni o tramite lacune).

Se il canale è già formato per tensione di gate nulla si parla di MOSFET a svuotamento

se per V<sub>GS</sub> = 0 V non si ha ancora il canale formato si parla di MOSFET a ad arricchimento

#### Se il MOSFET è a svuotamento (canale n)

Si ha un intenso passaggio di corrente anche per tensione di gate Vg=0

La tensione di soglia del MOSFET è negativa

#### Se il MOSFET è ad arricchimento (canale n)

Non si ha passaggio di corrente per tensione di gate Vg=0

la tensione di soglia è positiva

#### Se il MOSFET è a svuotamento (canale p)

Si ha un intenso passaggio di corrente anche per tensione di gate Vg=0

La tensione di soglia del MOSFET è positiva

#### Se il MOSFET è ad arricchimento (canale p)

Non si ha passaggio di corrente per tensione di gate Vg=0

la tensione di soglia è negativa

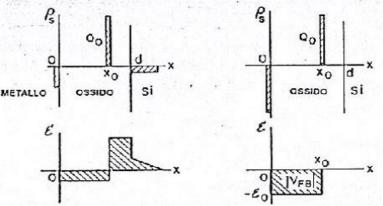

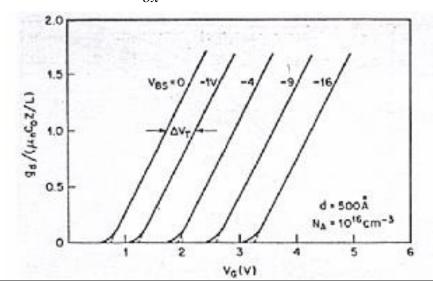

### Effetto della polarizzazione del substrato

Supponiamo che inizialmente  $V_{BS} = 0$  e sia  $V_{GS}$  tale da indurre nel semiconduttore la zona di inversione.

Questo significa che all'interfaccia tra semiconduttore e ossido ci sarà un certo valore di potenziale,  $\psi_x$  (>  $2\psi_B$ ), che assicura lo stato di inversione del semiconduttore.

Se ora applichiamo  $V_{\rm BS}$  < 0, risulta che al source ci sia un potenziale positivo rispetto al bulk

ovvero attrattivo per gli elettroni del canale, che possono uscire dal canale e riversarsi nel contatto di source.

Perciò, pur non essendo variato  $V_{GS}$ , il canale si trova "meno in inversione" rispetto al caso  $V_{BS}=0$

# La tensione di soglia

Per ripristinare la situazione iniziale occorre perciò aumentare  $V_{GS}$ .

Di quanto?

Per capirlo possiamo ragionare in questo modo:

accettori).

Quando si applica  $V_{GS}$  al gate, si induce sul gate una carica

valore della tensione di soglia.

Applicando V<sub>BS</sub> si aumenta la carica della regione svuotata a spese

positiva che viene compensata dalla carica negativa del

semiconduttore, contenuta in parte nel canale (costituita da

elettroni) e in parte nella regione svuotata (costituita da ioni

della carica del canale

La carica di gate da compensare rimane la stessa!!

Perciò attraverso l'espressione della carica indotta nella regione di svuotamento in funzione della tensione, si può risalire al nuovo

# La tensione di soglia con $V_{BS}\neq 0$

$$Q_B = \sqrt{2q\varepsilon_S N_A (2\psi_B - V_{BS})}$$

$$V_{T0} = \frac{\sqrt{2q\varepsilon_{S}N_{A}(2\psi_{B})}}{C_{ox}} + 2\psi_{B} + V_{FB}$$

$$\sqrt{2q\varepsilon_{S}N_{A}(2\psi_{B} - V_{PS})}$$

$$V_{T1} = \frac{\sqrt{2q\varepsilon_S N_A (2\psi_B - V_{BS})}}{C_{ox}} + 2\psi_B + V_{FB}$$

$$\Delta V_{T} = V_{T1} - V_{T0} = \frac{\sqrt{2q\varepsilon_{S}N_{A}}}{C_{ox}} (\sqrt{2\psi_{B} - V_{BS}} - \sqrt{2\psi_{B}})$$

# Il PMOS con $V_{FB}\neq 0$ e $V_{BS}\neq 0$

In un MOSFET a canale p, di solito viene applicata al bulk la più alta tra le tensioni applicate agli altri terminali ovvero tensioni ≥0

Al source ci sia un potenziale negativo rispetto al bulk

attrattivo per le lacune del canale, che possono uscire dal canale e riversarsi nel contatto di source.

Perciò, pur non essendo variato  $V_{GS}$ , il canale si trova "meno in inversione" rispetto al caso  $V_{SB}=0$

$$\begin{split} V_T &= -\frac{\sqrt{2q\varepsilon_S N_D}}{C_{ox}} \sqrt{2\psi_B - V_{SB}} - 2\psi_B + V_{FB} \\ \Delta V_T &= -\frac{\sqrt{2q\varepsilon_S N_D}}{C_{ox}} (\sqrt{2\psi_B - V_{SB}} - \sqrt{2\psi_B}) \\ V_{T1} &= V_{T0} - \frac{\sqrt{2q\varepsilon_S N_D}}{C_{ox}} (\sqrt{2\psi_B - V_{SB}} - \sqrt{2\psi_B}) \end{split}$$

# Scaling dei dispositivi

Negli ultimi decenni abbiamo assistito ad un costante e continuo aumento delle prestazioni dei differenti dispositivi elettronici, accompagnate da una continua diminuzione dei costi.

Aumentare le prestazioni significa aumentare il numero di processi che un processore è in grado di svolgere per unità di area e unità di tempo, da cui, integrazione maggiore e velocità di calcolo maggiore.

Maggiore integrazione significa fare in modo che il numero di transistor per unità di area aumenti.

Il che, sostanzialmente, significa

#### DIMINUIRE LE DIMENSIONI DEI TRANSISTOR

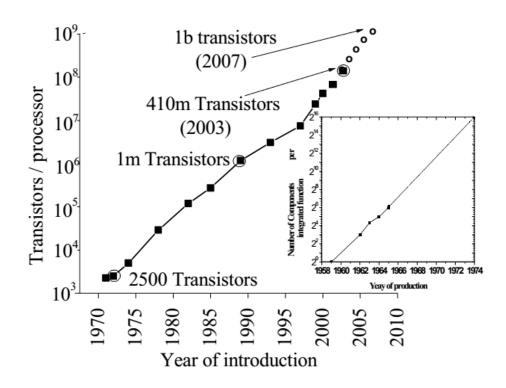

Il primo ad occuparsi, ed in un certo modo, teorizzare questo processo di continua miniaturizzazione dei dispositivi fu Gordon Moore nel lontano 1965.

Moore, in uno dei suoi articoli più famosi, sostenne che il numero di transistor per unità di area sarebbe aumentato costantemente nei 10 anni successivi, raddoppiando ogni anno

Quando Moore scrisse questo articolo, il numero di transistor per chip era 32, effettivamente, nel 1975 il numero di transistor arrivò a quasi 10<sup>5</sup>!!

Questa legge venne chiamata Legge di Moore, e, seppur con alcune modifiche, è ancora valida

Nel corso degli ultimi anni abbiamo quindi assistito ad un continuo processo di innovazione tecnologica, mirato all'ottimizzazione dei processi fabbricativi per l'ottenimento di MOSFET di dimensioni sempre più piccole

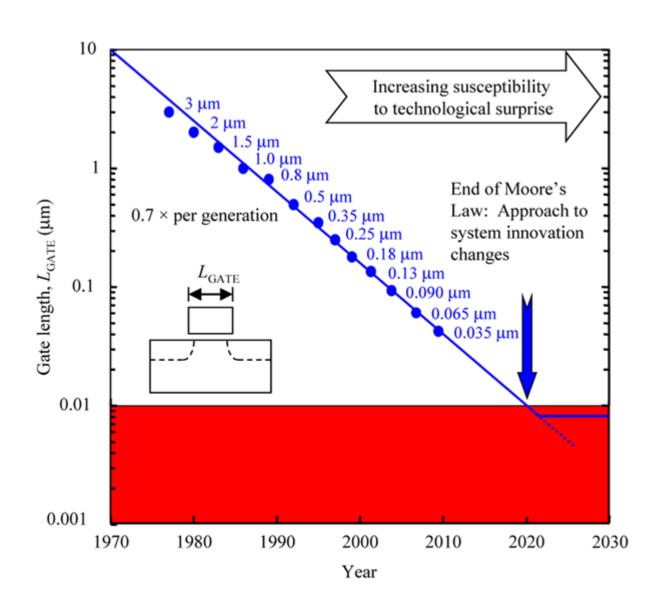

Negli anni '90 le dimensioni di canale tipiche di un MOSFET era intorno ai 2  $\mu m$

Già negli anni 2000 le dimensioni si sono ridotte ben al di sotto del micron.

Si è entrati nell'era delle tecnologie submicrometriche

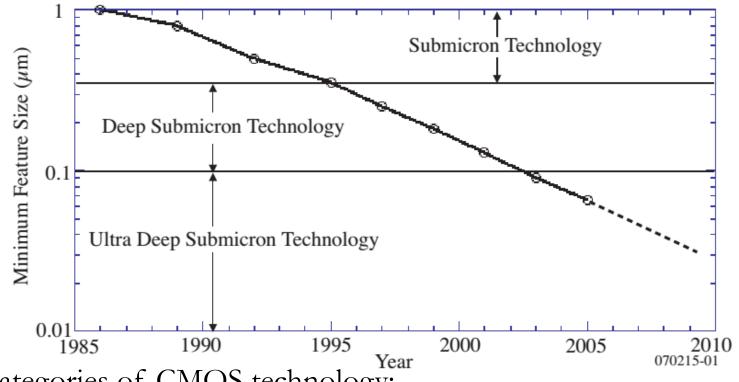

# Deep and UltraDeep sub-micrometer MOS

Categorization of CMOS Technology

Minimum feature size as a function of time:

- Categories of CMOS technology:

- Submicron technology Lmin > 0.35 microns

- Deep Submicron technology (DSM)  $-0.1 \mu m \le Lmin \le 0.35 \mu m$

- Ultra-Deep Submicron technology (UDSM) Lmin  $\leq 0.1 \, \mu \text{m}$